# SWITCHING SANJAYA MANIKTALA POWET SUPPLIES

A to Z

# Switching Power Supplies A to Z

# Switching Power Supplies A to Z Sanjaya Maniktala

Newnes

Newnes is an imprint of Elsevier

Newnes is an imprint of Elsevier 30 Corporate Drive, Suite 400, Burlington, MA 01803, USA Linacre House, Jordan Hill, Oxford OX2 8DP, UK

Copyright © 2006, Elsevier Inc. All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher.

Permissions may be sought directly from Elsevier's Science & Technology Rights Department in Oxford, UK: phone: (+44) 1865 843830, fax: (+44) 1865 853333, E-mail: permissions@elsevier.com. You may also complete your request on-line via the Elsevier homepage (http://elsevier.com), by selecting "Support & Contact" then "Copyright and Permission" and then "Obtaining Permissions."

Recognizing the importance of preserving what has been written, Elsevier prints its books on acid-free paper whenever possible.

### Library of Congress Cataloging-in-Publication Data

Application Submitted

### **British Library Cataloguing-in-Publication Data**

A catalogue record for this book is available from the British Library.

ISBN 13: 978-0-7506-7970-1 ISBN 10: 0-7506-7970-0

For information on all Newnes publications visit our Web site at www.books.elsevier.com

$06\ 07\ 08\ 09\ 10\ \ 10\ 9\ 8\ 7\ 6\ 5\ 4\ 3\ 2\ 1$

Printed in the United States of America

# Working together to grow libraries in developing countries

www.elsevier.com | www.bookaid.org | www.sabre.org

**ELSEVIER**

BOOK AID

Sabre Foundation

# **Contents**

| Preface                                                                          | X   |

|----------------------------------------------------------------------------------|-----|

| Acknowledgements                                                                 | xvi |

| Chapter 1: The Principles of Switching Power Conversion                          | 1   |

| Introduction                                                                     | 3   |

| Overview and Basic Terminology                                                   | 5   |

| Understanding the Inductor                                                       | 22  |

| Evolution of Switching Topologies                                                | 43  |

| Chapter 2: DC-DC Converter Design and Magnetics                                  | 61  |

| DC Transfer Functions                                                            | 64  |

| The DC Level and the "Swing" of the Inductor Current Waveform                    | 65  |

| Defining the AC, DC, and Peak Currents                                           | 68  |

| Understanding the AC, DC and Peak Currents                                       | 70  |

| Defining the "Worst-case" Input Voltage                                          | 72  |

| The Current Ripple Ratio 'r'                                                     | 75  |

| Relating <i>r</i> to the Inductance                                              | 75  |

| The Optimum Value of r                                                           | 77  |

| Do We Mean Inductor? Or Inductance?                                              | 79  |

| How Inductance and Inductor Size Depend on Frequency                             | 80  |

| How Inductance and Inductor Size Depend on Load Current                          | 80  |

| How Vendors Specify the Current Rating of an Off-the-shelf Inductor and          |     |

| How to Select It                                                                 | 81  |

| What Is the Inductor Current Rating We Need to Consider for a Given Application? | 82  |

| The Spread and Tolerance of the Current Limit                                    | 85  |

| Worked Example (1)                                                               | 88  |

| Worked Examples (2, 3, and 4)                                                    | 100 |

| Worked Example (5) — When Not to Increase the Number of Turns                    | 106 |

| Worked Example (6) — Characterizing an Off-the-shelf Inductor in a               |     |

| Specific Application                                                             | 110 |

| Calculating the "Other" Worst-case Stresses                                      | 118 |

# Contents

| Chapter 3: Off-line Converter Design and Magnetics                | 7  |

|-------------------------------------------------------------------|----|

| Flyback Converter Magnetics                                       | 30 |

| Forward Converter Magnetics                                       | 52 |

| Chapter 4: The Topology FAQ                                       | 7  |

| Questions and Answers                                             | 19 |

| Chapter 5: Conduction and Switching Losses                        | 3  |

| Switching a Resistive Load                                        | )6 |

| Switching an Inductive Load                                       | 0  |

| Switching Losses and Conduction Loss                              | 3  |

| A Simplified Model of the Mosfet for Studying Inductive Switching |    |

| Losses                                                            | 5  |

| The Parasitic Capacitances Expressed in an Alternate System       | 7  |

| Gate Threshold Voltage                                            | 8  |

| The Turn-on Transition                                            | 8  |

| The Turn-off Transition                                           | 22 |

| Gate Charge Factors                                               | 24 |

| Worked Example                                                    | 27 |

| Applying the Switching Loss Analysis to Switching Topologies      | 31 |

| Worst-case Input Voltage for Switching Losses                     | 32 |

| How Switching Losses Vary with the Parasitic Capacitances         | 3  |

| Optimizing Driver Capability vis-à-vis Mosfet Characteristics     | 34 |

| Chapter 6: Printed Circuit Board Layout                           | 7  |

| Introduction                                                      | 39 |

| Trace Section Analysis                                            | 39 |

| Some Points to Keep in Mind During Layout                         | 10 |

| Thermal Management Concerns                                       | 17 |

| Chapter 7: Feedback Loop Analysis and Stability 24                | 9  |

| Transfer Functions, Time Constant and the Forcing Function        | 51 |

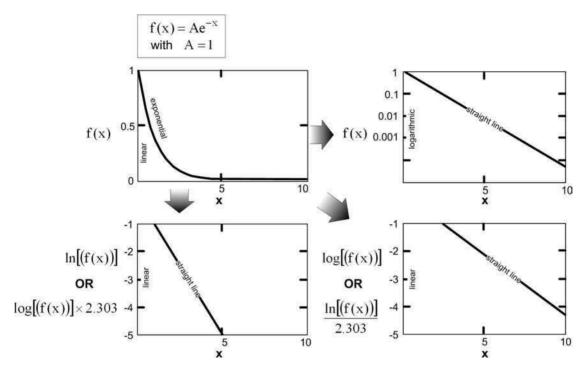

| Understanding 'e' and Plotting Curves on Log Scales               | 52 |

| Time Domain and Frequency Domain Analysis                         | 55 |

| Complex Representation                                            | 6  |

| Nonrepetitive Stimuli                                             | 8  |

| The s-plane                                                       | 8  |

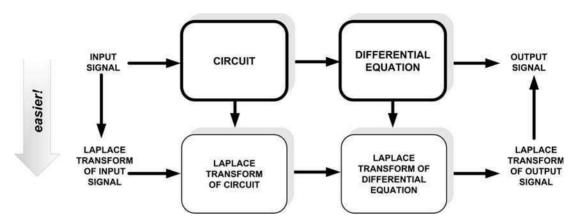

| Laplace Transform                                                 | 60 |

| Disturbances and the Role of Feedback                    | 262 |

|----------------------------------------------------------|-----|

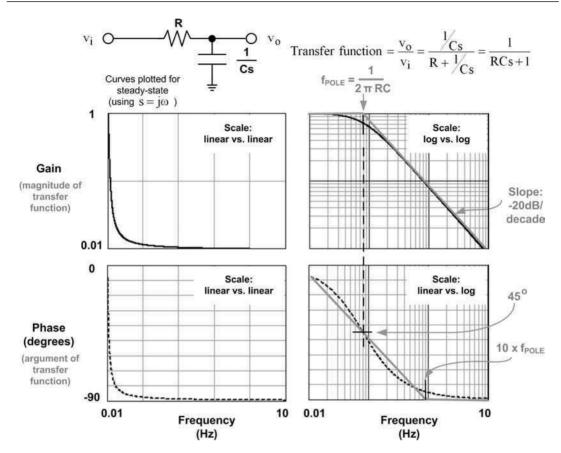

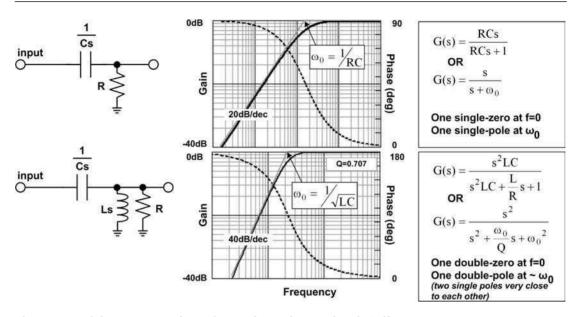

| Transfer Function of the RC Filter                       | 264 |

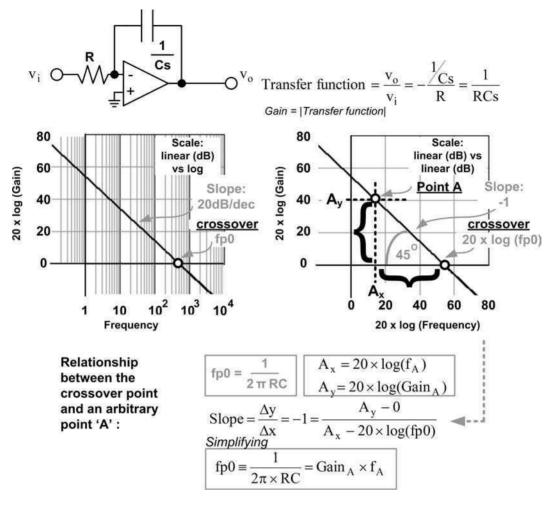

| The Integrator Op-amp ("pole-at-zero" filter)            | 267 |

|                                                          | 269 |

|                                                          | 270 |

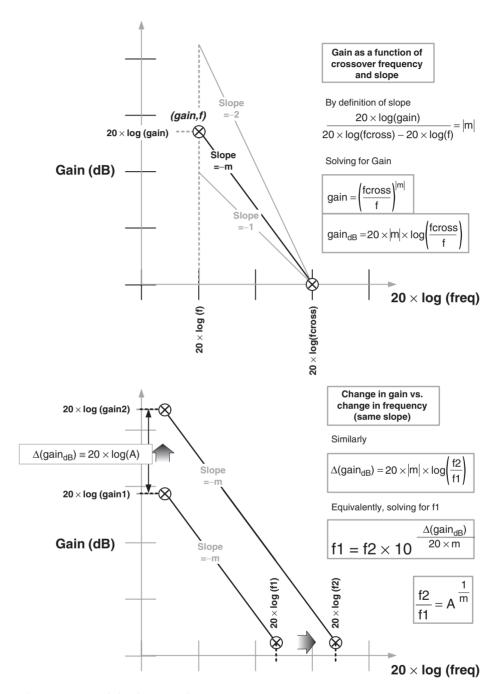

| Summary of Transfer Functions of Passive Filters         | 273 |

|                                                          | 274 |

| Interaction of Poles and Zeros                           | 276 |

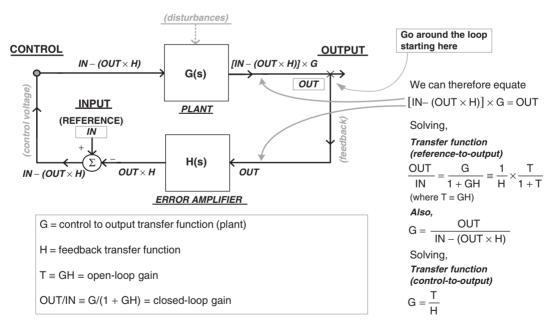

| Closed and Open Loop Gain                                | 277 |

| The Voltage Divider                                      | 280 |

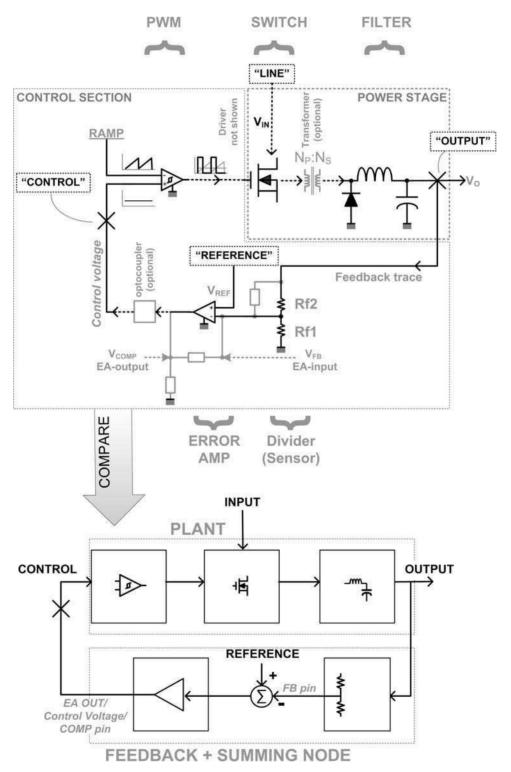

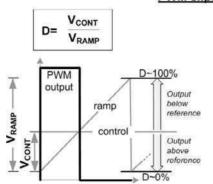

| Pulse Width Modulator Transfer Function (gain)           | 281 |

| Voltage Feedforward                                      | 282 |

| Power Stage Transfer Function                            | 283 |

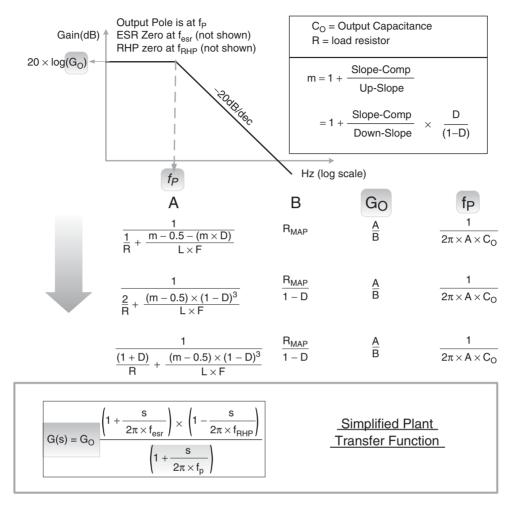

| Plant Transfer Functions of All the Topologies           | 284 |

| Boost Converter                                          | 286 |

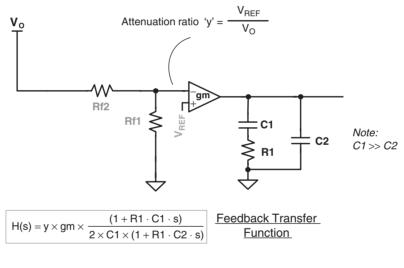

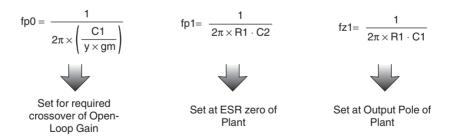

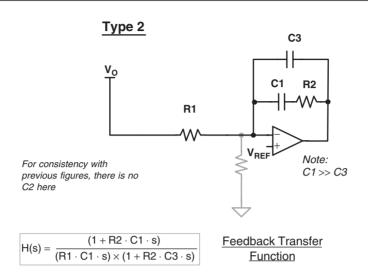

| Feedback Stage Transfer Functions                        | 289 |

| Closing the Loop                                         | 291 |

| Criteria for Loop Stability                              | 293 |

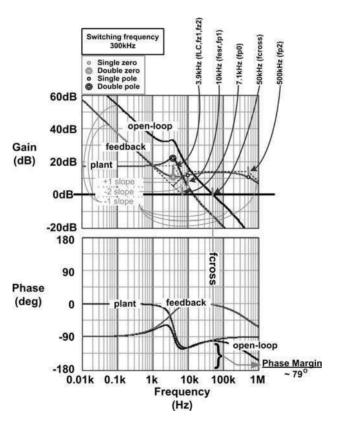

| Plotting the Open-loop Gain and Phase with an Integrator | 293 |

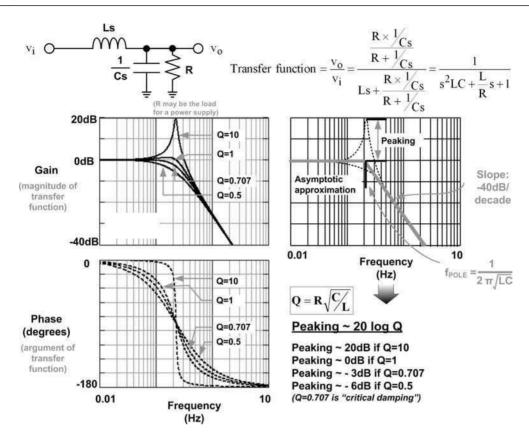

| Canceling the Double Pole of the LC Filter               | 295 |

| The ESR Zero                                             | 296 |

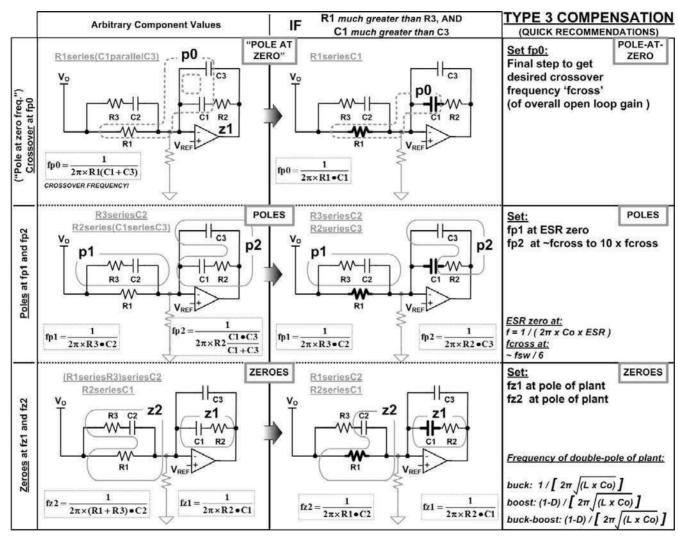

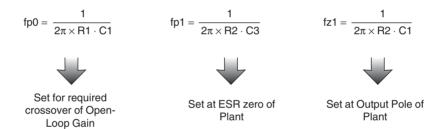

| Designing a Type 3 Op-amp Compensation Network           | 297 |

| Optimizing the Feedback Loop                             | 301 |

| Input Ripple Rejection                                   | 304 |

| Load Transients                                          | 305 |

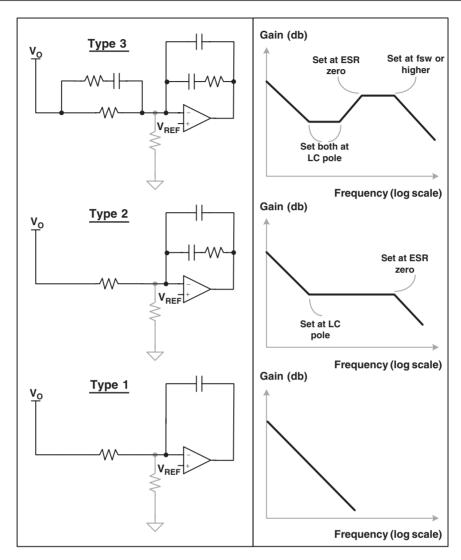

| Type 1 and Type 2 Compensations                          | 306 |

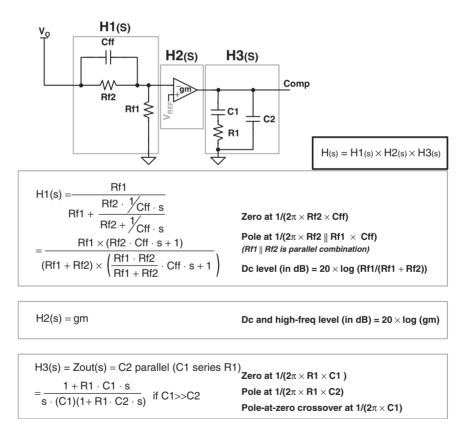

| Transconductance Op-amp Compensation                     | 308 |

| Simpler Transconductance Op-amp Compensation             | 311 |

| Compensating with Current Mode Control                   | 313 |

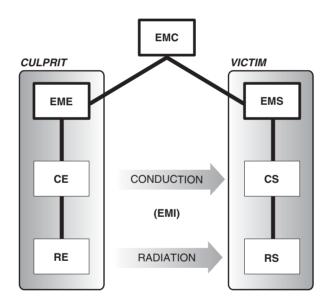

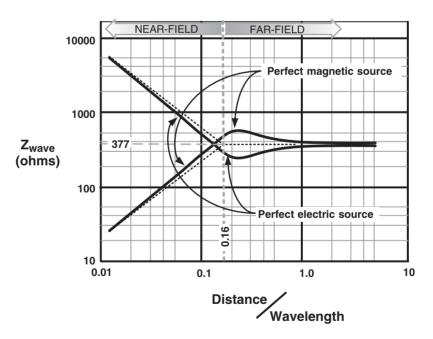

| Chapter 8: EMI from the Ground up — Maxwell to CISPR     | 23  |

| The Standards                                            | 326 |

| Maxwell to EMI                                           | 328 |

| Susceptibility/Immunity                                  | 333 |

| • •                                                      | 335 |

| EMI for Subassemblies                                    | 335 |

| CISPR 22 for Telecom Ports — Proposed Changes            | 336 |

# Contents

| Chapter 9: Measurements and Limits of Conducted EMI                     | 339 |

|-------------------------------------------------------------------------|-----|

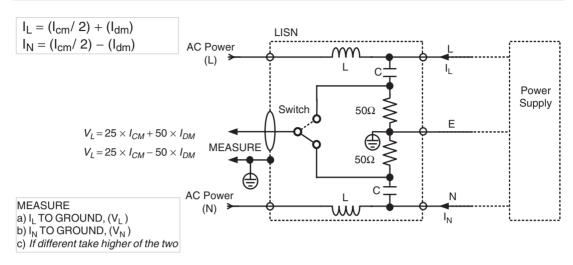

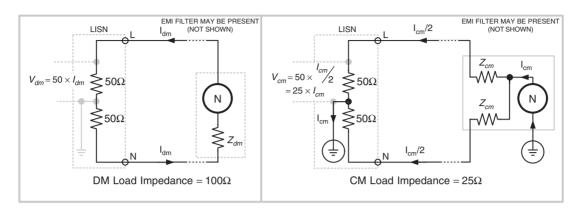

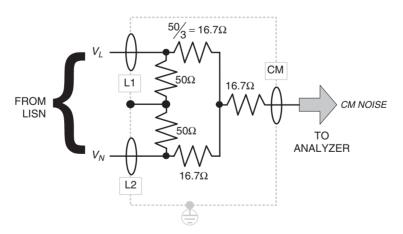

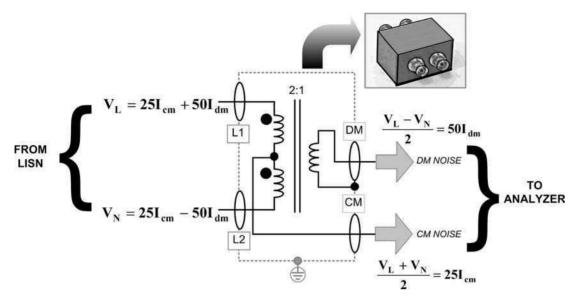

| Differential Mode and Common Mode Noise                                 | 341 |

| How Conducted EMI Is Measured                                           | 344 |

| The Conducted Emission Limits                                           | 348 |

| Quasi-peak, Average, and Peak Measurements                              | 351 |

| Chapter 10: Practical EMI Line Filters                                  | 355 |

| Safety Issues in EMI Filter Design                                      | 357 |

| Practical Line Filters                                                  | 359 |

| Safety Restrictions on the Total Y-capacitance                          | 367 |

| Equivalent DM and CM Circuits                                           |     |

| Some Notable Industry Experiences in EMI                                | 371 |

| Chapter 11: DM and CM Noise in Switching Power Supplies                 | 373 |

| Main Source of DM Noise                                                 | 375 |

| The Main Source of CM Noise                                             | 377 |

| The Ground Choke                                                        | 385 |

| Chapter 12: Fixing EMI across the Board                                 | 387 |

| The Role of the Transformer in EMI                                      | 389 |

| EMI from Diodes                                                         | 394 |

| Beads, and an Industry Experience — the dV/dt of Schottky Diodes        | 397 |

| Basic Layout Guidelines                                                 | 398 |

| Last-ditch Troubleshooting                                              |     |

| Are We Going to Fail the Radiation Test?                                | 402 |

| Chapter 13: Input Capacitor and Stability Considerations in EMI Filters | 403 |

| Is the DM Choke Saturating?                                             | 405 |

| Practical Line Filters in DC-DC Converter Modules                       | 410 |

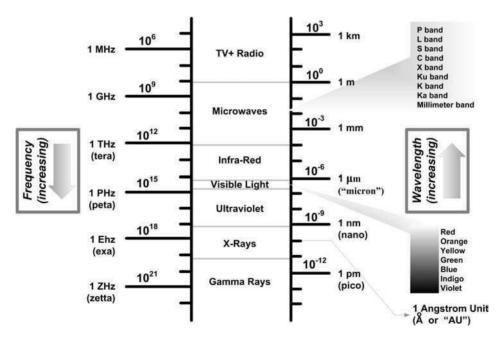

| Chapter 14: The Math behind the Electromagnetic Puzzle                  | 417 |

| Math Background — Fourier Series                                        | 419 |

| The Rectangular Wave                                                    | 420 |

| Analysis of the Rectangular Wave                                        | 423 |

| The Trapezoid                                                           |     |

| The EMI from a Trapezoid                                                | 426 |

| The Road to Cost-effective Filter Design                                |     |

| Practical DM Filter Design                                              |     |

| Practical CM Filter Design                                              | 433 |

| Appendix 1: Focusing on Some Real-world Issues                                  | , |

|---------------------------------------------------------------------------------|---|

| Sounds Like Worst-case, But There's Danger Lurking in the Middle                | ) |

| Loop Design Sometimes Compensates for Lower-quality Switchers 440               | ) |

| Re-inventing the Wheel as a Square                                              | ) |

| The Mighty Zener                                                                | ļ |

| Better Do the Math: Ignore Transfer Functions at Your Own Peril                 | 7 |

| Aluminum Cap Multipliers — Why We Can't Have Them and Eat Them Too 449          | ) |

| Limit Your Peak Current, Not Your Reliability                                   | ) |

| Reliability Is No Flash in the Pan                                              | į |

| The Incredible Shrinking Core                                                   | ) |

| Plain Lucky We Don't Live in a PSpice World!                                    | ) |

| Why Does the Efficiency of My Flyback Nose-dive?                                | , |

| It's Not a Straight Line: Computing the Correct Drain to Source Resistance from |   |

| V-I Curves                                                                      | ) |

| Don't Have a Scope? Use a DMM, Dummy!                                           | ) |

| Are We Making Light of Electronic Ballasts?                                     | , |

| More on Designing Reliable Electronic Ballasts                                  | , |

| The Organizational Side of Power Management: One Engineer's Perspective         | ) |

| Appendix 2: Reference Design Table                                              | ; |

| References                                                                      | ) |

| Index 493                                                                       | 2 |

# **Preface**

Looking back, I realize there was actually never an exact moment when I said to myself "I have had it with Physics — let me do Electronics now"! My near mid-life career change was a rather gradual process. Faced with an exponentially declining interest in pi-mesons, Lagrangian multipliers, quantum electrodynamics, and so on, my grades had started scraping the bottom of the barrel. It didn't help that I perceived my last bunch of professors to be largely apathetic to students in general — it seemed that teaching just happened to be what they *needed* to keep doing, to be *eligible* for research grants, which is what they *really* enjoyed doing. And Physics itself, for all its initial undergraduate allure, had at the post-graduate level, turned suddenly very mathematical and abstruse, contradicting my inherent desire to be firmly embedded in reality (not virtual reality). Unfortunately, the disenchantment reached a culmination only during my second Masters degree program, in Chicago. Too late! So though I eventually did part company with Physics (as good friends, I may add), there was a slight problem — I didn't have a clue what to do next. I call that my *Problem Number 1*.

Back in hot, bustling and dusty India, it took me several years to figure things out. But finally, I did! The small bags of transistors, capacitors, resistors and inductors that I had lately started tinkering with, held the answer to all my problems. And hope for the future. This was my long-awaited lifeboat. I could now feel, touch, build and test whatever I did. No deceptive sense of comfort lolling around in lush minefields of equations and algebraic abstractions. This was the real world, the one that we live in every day.

Problem Number 2: I still didn't know the ABCs (or the NPNs) of electronics. So I had to teach myself very gradually, working days and often very late into the nights, barely stopping only to ask the elderly local components dealer, daring questions like — what is a transistor?! This act went on for a pretty long time — in fact I became the Rocky Horror Midnight show — you got to see me mostly at midnight for several years in succession. But it would have still been impossible if I had not met a few very remarkable men along the way (see Acknowledgements). Finally, with all the help at my disposal (most of it mine), I think I made it into the exciting world of electronics. And into power electronics. Aha! I could start rolling down the shutters now. Or could I?

хi

The above chain of hair-raising events is the one and only reason this book ever got written in the first place!

But wait! I have explained "how" this book got written, but did I explain why? Actually I haven't yet. Because that has something to do with the last major problem I faced. I call it Problem Number 3 — encountering people who knowingly or unknowingly thwart the growth of the engineering discipline that gives us growth. Now, I had personally been through a rather life-changing process (of being rescued by Electronics). So perhaps it was more natural for me to always think I owed Electronics my best, in return for favors received. But I realize not everyone thinks along those lines, at least not all the time. Maybe they had affluent fathers paying for their shiny EE degrees from MIT or Yale. But I didn't have an affluent father nor an EE degree. However, at some stage, we all have to realize that we share the same forces of nature, and a common stake in its existence and further development. Our destiny is eventually common, and therefore we have a common responsibility to uphold it too. Anybody who has learnt enough about the immense mystical forces of nature realizes that he or she has really learnt nothing at all. It will therefore be very surprising if they don't end up imbibing the sense of humility that Newton once expressed in the following words:

"I know not what I may appear to the world, but to myself I seem to have been only like a boy playing on the sea-shore, and diverting myself in now and then finding a smoother pebble or a prettier shell, whilst the great ocean of truth lay all undiscovered before me."

Power Electronics too, is just a small part of that infinitesimal part of the universe that we have just begun to understand. There is much, much more, just waiting to be discovered. Should we be the ones to encourage that onward natural process, or thwart it (even momentarily) with our petty office-space personal agendas?

Finally, when I had seen too much and heard too much, I wrote the following paragraphs somewhere on the web, in what is now a rather controversial opinion piece for some people who obviously don't understand the logic or the motivation for it (see last page of Appendix 1)

'Technology may never gain a foothold in a "king's court," where you are either rewarded with largesse for being vehemently agreeable, or unceremoniously sentenced to the dark dungeons for the rest of your life. Engineers like to speak out - but usually only when they were sure of their facts and have incontrovertible data to back themselves up. They therefore deserve and need a "peer environment," where they are judged (primarily) by the respect received from their peers — the king be damned (on occasion)!

It must be kept in mind that this can really bother the king sometimes! So managers who supervise engineers, should be fairly competent at a technical level themselves and respect data and facts equally. They can't attempt to win a technical argument by throwing rank on

their subordinates. Nor should they ever go around, God forbid, trying to subsequently shoot the "emotional and/or disrespectful" engineer down ("that'll teach him"). Surprisingly that does happen more than we dare admit. Not only does the good engineer pay the price, but so does technology in the long run.'

The only reason that this piece (based largely on the old wisdom of my dear long-time mentor and former-former Boss Dr GT Murthy) turned controversial was I suspect, because it had hit closer to home than even I had imagined. It is always amusing that whenever someone has one-too-many skeletons in their closets, the very sound of a distant siren triggers off their worst fears. I was told to stop talking about things I didn't understand, and stick to my (humble) circuits. I was also refused the normal official Author Encouragement Program payment that I thought was due to me as per their guidelines — for this article and even for my other popular power electronics book, which they had already used freely to promote their products. Finally the best thing I did was to quit as soon as I could! Without notice. Then surprise, surprise! Just after I resigned, they went and restructured exactly as I had been preaching all along — by re-amalgamating their two erstwhile groups "Portable Power" and "Power Management" into one, saying privately that there would be "more sharing among the engineers finally". My words exactly (read the article)! Weighing all these events in mind, I found some peace knowing the net result of my article was that a few better-designed, more peer-reviewed products would ultimately emerge from the very same company in question (whether they cared to admit it or not). For sure, the winner wasn't me, certainly not some insecure small-minded manager in a hopelessly high position. It was electronics that had had its day. And that was enough for me.

Till a while ago, I had naively thought large corporations, especially those showcasing themselves in glitzy facilities headquartered in Silicon Valley, had woken up to the times and become more professionally managed. To me that meant things like not allowing race-related slurs to demoralize struggling engineers, not allowing chilling war-rhetoric indiscriminately sent via company E-mail (making employees wary of their own supervisor's basic sanity at times), and simply, simply, just rewarding all efforts fairly and without discrimination. Too much to ask! I wasn't too sure anymore that the *field* of electronics, the one that I was trying so hard to nurture, was getting even close to what it deserved. Sure, they had now started declaring "record gross margins" and so on. But behind this benumbing onslaught of pure PR, you have to remember that that their new-found exhilaration was a) borne mainly on the shoulders of a new breed of extremely talented, friendly and pro-active engineers and b) basically, they just stopped loss-making operations, in areas that were outside their "core competence" (in reality: those business units that had been so badly managed from start to finish, that even the engineers couldn't make a difference anymore). Further, almost without further thought, they kept laying-off several talented or promising engineers, some that I knew personally — often because their own managers had screwed up so bad they needed alibis to present before their equally bad supervisors, who needed alibis to present to

www.IranSwitching.ir xiii

theirs .... and so on. Of course the last man standing was apparently just too busy counting the millions of dollars cash bonus he had just received for meeting the company's (short-term?) "targets". End of story. Not a tear for those engineers that were walked out one fine day a) without the slightest warning b) without even being given an opportunity to present their side of the story — quite unlike even a normal court of law anywhere in the world. I asked myself — what if Newton or Einstein had been similarly dogged by incompetent dishonest supervisors? Would the world have been a better place today? And come to think of it, how many potential Newtons and Einsteins had these companies already banned into the hell of dark obscurity, and possibly premature retirement, while chanting that their analog ICs were *nature incarnate* ("the sight and sound of information")? We never know the real casualty toll ever, do we?

As you can see, I can honestly say I have not found the solution to *Problem Number 3* yet. But I am still trying! And this book is an effort to do just that.

So now, it is time to tell you what exactly I have tried to achieve with this book. One unique aspect about designing power supplies is that the "devil is in the details". In other words, I, as a technical writer, can either put in everything, including the supporting Math, and come up with a book that (only) professionals would like. Or I could try making it very simple and straightforward for the beginner. But then the chances are very high I would miss out on the very essence of what power supply design is all about — the optimization, and design trade-offs. To strike a meaningful compromise between simplicity and depth requires a very carefully considered structure of presentation, one that I have really tried hard to achieve in this book. For example, several books out there, try to give a step-by-step detailed design procedure for DC-DC converters. However, they seem to routinely miss out on the important fact that the input is rarely, if ever, a "single-point" input voltage level. It is usually a "wide-range input" and we need to be very clear which converter stresses are at their worst at the highest end of the input, and which ones at the lowest input end. We also need to know which stresses we need to give priority to during a particular design step within that procedure. Clearly, designing a good power supply is not a trivial task! In Chapter 2 I have presented a universal design procedure for DC-DC converters that hopefully fulfills the simultaneous demands of rigorous detail as well as simplicity.

So what did we do in Chapter 1? That to most readers is just an introduction that they can readily skim over. Wrong! Let's take a step (and page) back. This particular introduction actually starts at the *component* level, not at the topology level as most other books do. The hope is that now, even a beginner, can understand the mysteries of a capacitor and inductor, then tie them up synergistically, to derive a switching converter topology. In fact, it will become clear that *all* topologies evolve out of a basic understanding of how, in particular, the *inductor* works. Here, advanced readers should beware. Because, while interviewing even

senior engineers for applications engineer positions, I found that many of them are still quite uncomfortable with the very concept of an inductor. Therefore, I think it is a good idea for every reader, novice or advanced, to read the book in the order of chapters presented, starting from the very first chapter. Just don't be caught reading it (by your perception-driven supervisor!). The temptation of jumping straight into an advanced chapter to "save time" may just end up slowing things down even more in the long run (besides causing avoidable bruising of self-confidence for some, along the way). Basic concepts always need to be brought in at the right time, exemplified, and then firmed up to last a lifetime.

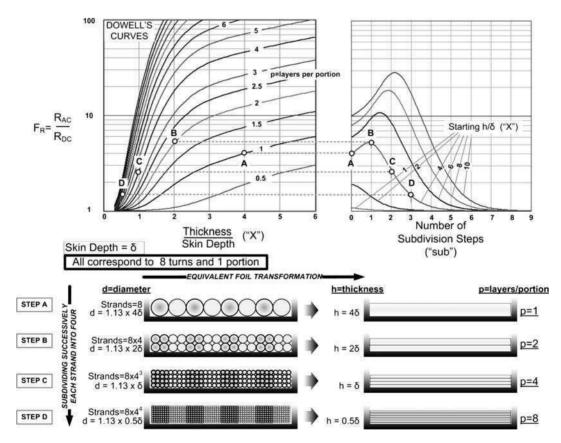

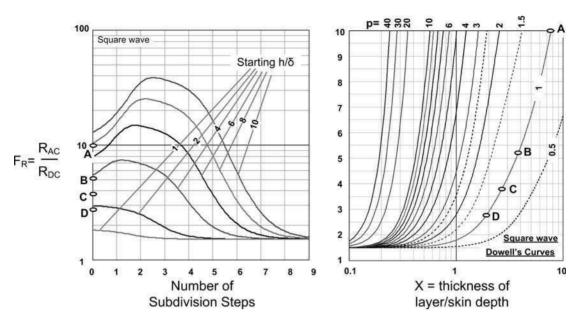

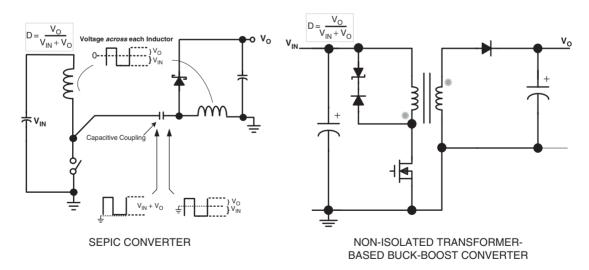

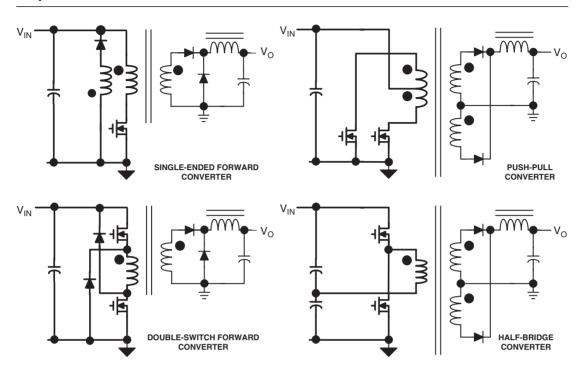

In Chapter 3 I have tried to start at a fairly basic level again, but then ramped up steeply to provide one of the most detailed step-by-step procedures available for designing off-line converters and their associated magnetics. This includes the dreaded Proximity Effect analysis. I have broken up the basic procedure into two separate iterative strategies — one for foil windings and another for round windings, because their respective optimization procedures are really very different. There are also generous amounts of curves and plots thrown in to quickly help the engineer visualize and design the magnetics optimally.

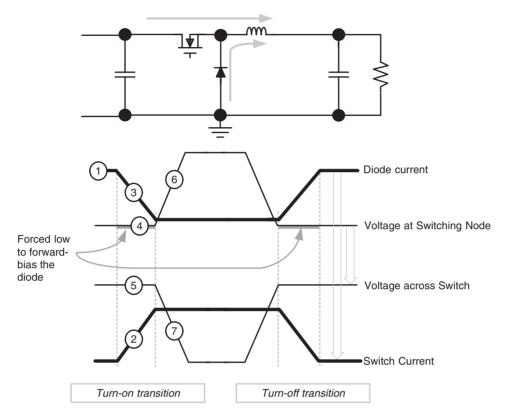

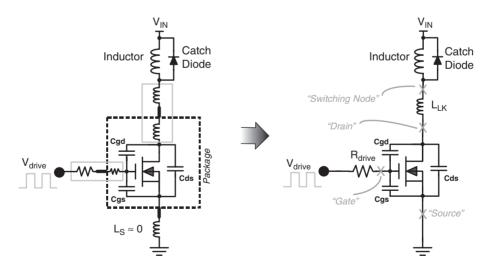

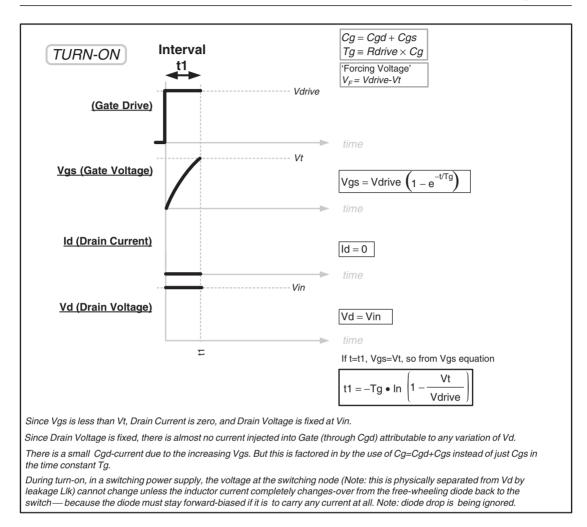

I have included a chapter devoted largely to switching losses in MOSFETs, since this topic has become increasingly vital as switching frequencies are increased. But it has been presented with some of the most carefully prepared and detailed graphics probably seen in related literature — highlighting each phase of the turn-on and turn-off individually. Common simplifying assumptions have also been made whenever appropriate, and the user should thereafter have no trouble anymore practicing this rather poorly understood area of power conversion. There is also some interesting parameterized graphical information available that can come in handy either for an applications engineer selecting external MOSFETs, or an IC designer trying to optimize the driver stages of the chip.

The chapter on loop stability is likewise presented from scratch to finish, with very detailed accompanying graphics. My hope is that for the first time the reader will have easy access to almost all the equations required for loop compensation. Now, even a novice, can very quickly get very deep into this area (as I once did).

There are also seven chapters on EMI, starting from the very basics and moving up to a full mathematical treatment. This is again a topic that has been almost studiously avoided in most related literature, and yet is needed so badly today. It needs much more elaboration I thought.

To cap it all, there is an "interview-friendly" FAQ, several Mathcad files, and various design spreadsheets thrown in.

As you can see, the book has been designed to try to live up to its name "A to Z". Of course that is never really going to be possible, least of all in an all-encompassing area such as Power Conversion. But hey, I did give it a shot! The stage is now set. I hope you like

# Preface

this book, even if it is A to Z with some of the alphabets missing along the way, and go on to make a small but noticeable difference, using it. Though I do strongly suggest you choose where you attempt to do it, because that that makes a big difference in the long run — to technology and to its committed practitioners: you the engineers. And of course, it is to you that this book is solely dedicated.

-Sanjaya Maniktala

# Acknowledgements

It all started rather innocuously. I walked into Dr GT Murthy's office one fine day, and changed my life. "Doc" was then the General Manager, Central R&D, of a very large electrical company headquartered in Bombay. In his new state-of-the-art electronics center, he had hand-picked some of India's best engineers (over a hundred already) ever assembled under one roof. Luckily, he too was originally a Physicist, and that certainly helped me gain some empathy. Nowadays he is in retirement, but I will always remember him as a thoroughly fair, honest and facts-oriented person, who led by example. There were several things I absorbed from him that are very much part of my basic engineering persona today. You can certainly look upon this book as an extension of what Doc started many years ago in India ... because that's what it really is! I certainly wouldn't be here today if I hadn't met Doc. And in fact, several of the brash, high-flying managers I've met in recent years, desperately need some sort of crash course in technology and human values from Doc!

Several people appeared a little later, aiding me along, especially when it mattered most. There was Stephan Ohr, the affable former Editor of Planet Analog who really believed in me, and gave me all my initial confidence as a writer. His personal writings too, inspired me a lot. Then there was Mike He, the former clever, pushy, and straight-talking PR person from National Semiconductor. Though Mike left rather quickly for another company, he still manages to keep in touch with me and encourage me along whenever necessary. There was also the likeable Charles Glaser ("Chuck") from Elsevier, who suddenly appeared on the scene, and believed right from the start that I could do it.

Among the technical people who reviewed major parts of this book before publication, and helped me improve it a lot is Harry Holt, a very bright senior *engineer* from National Semiconductor. Harry's eagle eye and absolutely frank technical feedback saved the day for me several times.

Other engineers I want to especially remember from my previous company, for adding immeasurably in one way or another to my peace and positive energy while writing this book, are: Linh Truong, Anne Lu, Michele Sclocchi, Thomas Mathews, Iain Mosley, Ricardo Capetillo, Maurice Eaglin, Shantha Natarajan, Jerry Zheng, Faruk Nome and Wallace Ly. At my present company, Freescale Semiconductor, I would like to thank our brilliant product

xvii

### Acknowledgements

definition team consisting of Tim Herklots and Tony Allen, besides of course my new straight-shooting (and completely sane for a change!) supervisor, Ken Lenks.

Thanks are also due to my old Marketing buddy at National Semiconductor, Ajithkumar Jain, who besides helping out with a few chapters here, had actually also helped me make up my mind years ago by describing unforgettable scenes he witnessed while on a business tour in South-Asia with the still-incumbent topmost brass — high-powered executives celebrating a successful deal, with overflowing country liquor laced with freshly poured snake blood, administered by extremely hospitable hostesses on their laps. And a multi-course dinner that all but Ajith consumed without batting an eyelid — including an entree consisting of braised puppies, their tiny tails still intact. None of this was ever intended to see the light of day. I suspect Doc wouldn't have approved of this new method of propelling analog chip technology into the future. In any case, Ajith made me realize that my future at least could never be intertwined with theirs for long.

Thanks are also due to Carl M. Soares of Elsevier, for picking up this project rather late from a suddenly departing Production Manager, and then very quietly and professionally turning it around, despite my occasional impatience.

Of course this book was completely impossible, certainly not within the time frame, were it not for the unending support and patience of my wonderful wife Disha and daughter Aartika. Not to forget the newest member of our family "Munchi". Nor the memory of dear Chippy and Monty, who gave me the strength to keep going, many many years ago. Once again, they all created the right circumstances at home for me to be able to pull this off through sleepless nights, without looking like some bleary-eyed economic refugee.

# CHAPTER

1

# The Principles of Switching Power Conversion

# The Principles of Switching Power Conversion

### Introduction

Imagine we are at some busy "metro" terminus one evening at peak hour. Almost instantly, thousands of commuters swarm the station trying to make their way home. Of course there is no train big enough to carry all of them *simultaneously*. So, what do we do? Simple! We *split* this sea of humanity into several *trainloads* — and move them out in rapid succession. Many of these outbound passengers will later transfer to alternative forms of transport. So for example, trainloads may turn into bus-loads or taxi-loads, and so on. But eventually, all these "packets" will merge once again, and a throng will be seen, exiting at the destination.

Switching power conversion is remarkably similar to a mass transit system. The difference is that instead of people, it is *energy* that gets transferred from one level to another. So we draw energy continuously from an "input source," *chop* this incoming stream into packets by means of a 'switch' (a transistor), and then transfer it with the help of components (inductors and capacitors), that are able to *accommodate* these energy packets and exchange them among themselves as required. Finally, we make all these packets merge again, and thereby get a smooth and steady flow of energy into the output.

So, in either of the cases above (energy or people), from the viewpoint of an *observer*, a stream will be seen entering, and a similar one exiting. But at an *intermediate* stage, the transference is accomplished by breaking up this stream into more *manageable packets*.

Looking more closely at the train station analogy, we also realize that to be able to transfer a given number of passengers *in a given time* (note that in electrical engineering, energy transferred in unit time is 'power') — either we need bigger trains with departure times spaced relatively far apart OR several *smaller* trains leaving in *rapid* succession. Therefore, it should come as no surprise, that in switching power conversion, we always try to *switch at high frequencies*. The primary purpose for that is to *reduce the size* of the energy packets, and thereby also the *size of the components* required to store and transport them.

Power supplies that use this principle are called 'switching power supplies' or 'switching power converters.'

'Dc-dc converters' are the basic building blocks of modern high-frequency switching power supplies. As their name suggests, they 'convert' an available dc (direct current) input voltage rail ' $V_{IN}$ ,' to another more *desirable or usable* dc output voltage level ' $V_O$ .' 'Ac-dc

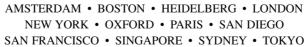

Figure 1-1: Typical Off-line Power Supply

converters' (see *Figure 1-1*), also called 'off-line power supplies,' typically run off the mains input (or 'line input'). But they first *rectify* the incoming sinusoidal ac (alternating current) voltage 'V<sub>AC</sub>' to a dc voltage level (often called the 'HVDC' rail, or 'high voltage dc rail') — which then gets applied at the input of what is essentially just *another dc-dc converter stage* (or derivative thereof). We thus see that power conversion is, in essence, almost always a *dc-dc voltage conversion process*.

But it is also equally important to create a *steady* dc output voltage level, from what can often be a widely *varying* and different dc input voltage level. Therefore, a 'control circuit' is used in all power converters to constantly monitor and compare the output voltage against an internal 'reference voltage.' Corrective action is taken if the output drifts from its set value. This process is called 'output regulation' or simply 'regulation.' Hence the generic term 'voltage regulator' for supplies which can achieve this function, switching or otherwise.

In a practical implementation, 'application conditions' are considered to be the applied input voltage  $V_{\rm IN}$  (also called the 'line voltage'), the current being drawn from the output,

4

that is,  $I_O$  (the 'load current') and the set output voltage  $V_O$ . Temperature is also an application condition, but we will ignore it for now, since its effect on the system is usually not so dramatic. Therefore, for a given output voltage, there are two specific application conditions whose variations can cause the output voltage to be immediately impacted (were it not for the control circuit). Maintaining the output voltage steady when  $V_{IN}$  varies over its stated operating range  $V_{INMIN}$  to  $V_{INMAX}$  (minimum input to maximum input), is called 'line regulation.' Whereas maintaining regulation when  $I_O$  varies over its operating range  $I_{OMIN}$  to  $I_{OMAX}$  (minimum to maximum load), is referred to as 'load regulation.' Of course, nothing is ever "perfect," so nor is the regulation. Therefore, despite the correction, there is a small but measurable change in the output voltage, which we call " $\Delta V_O$ " here. Note that mathematically, line regulation is expressed as " $\Delta V_O/V_O \times 100\%$  (implicitly implying it is over  $V_{INMIN}$  to  $V_{INMAX}$ )." Load regulation is similarly " $\Delta V_O/V_O \times 100\%$ " (from  $I_{OMIN}$  to  $I_{OMAX}$ ).

However, the *rate* at which the output can be corrected by the power supply (under *sudden* changes in line and load) is also important — since no physical process is "instantaneous" either. So the property of any converter to provide quick regulation (correction) under external disturbances is referred to as its 'loop response.' Clearly, the loop response is as before, a combination of its 'step-load response' and its 'line transient response.'

As we move on, we will first introduce the reader to some of the most basic terminology of power conversion and its key concerns. Later, we will progress toward understanding the behavior of the most vital component of power conversion — the *inductor*. It is this component that even some relatively experienced power designers still have trouble with! Clearly, real progress in any area cannot occur without a clear understanding of the components and basic concepts involved. Therefore, only after understanding the *inductor* well, will we go on to demonstrate that switching converters themselves are not all that mysterious either — in fact they evolve quite naturally out of our newly acquired understanding of the inductor.

# Overview and Basic Terminology

### **Efficiency**

Any regulator carries out the process of power conversion with an 'efficiency,' defined as

$$\eta = \frac{P_O}{P_{IN}}$$

where Po is the 'output power,' equal to

$$P_O = V_O \times I_O$$

and P<sub>IN</sub> is the 'input power,' equal to

$$P_{IN} = V_{IN} \times I_{IN}$$

Here, I<sub>IN</sub> is the average or dc current being drawn from the source.

Ideally we want  $\eta=1$ , and that would represent a "perfect" conversion efficiency of 100%. But in a *real* converter, that is with  $\eta<1$ , the *difference* ' $P_{IN}-P_{O}$ ' is simply the wasted power " $P_{loss}$ ," or 'dissipation' (occurring within the converter itself). By simple manipulation we get

$$\begin{aligned} P_{loss} &= P_{IN} - P_{O} \\ P_{loss} &= \frac{P_{O}}{\eta} - P_{O} \\ P_{loss} &= P_{O} \times \left(\frac{1 - \eta}{\eta}\right) \end{aligned}$$

This is the loss expressed in terms of the output power. In terms of the input power we would similarly get

$$P_{loss} = P_{IN} \times (1 - \eta)$$

The loss manifests itself as *heat* in the converter, which in turn causes a certain measurable 'temperature rise'  $\Delta T$  over the surrounding 'room temperature' (or 'ambient temperature'). Note that high temperatures affect the *reliability* of all systems — the rule-of-thumb being that every 10°C rise causes the failure rate to double. Therefore, part of our skill as designers is to reduce this temperature rise, and thereby also achieve higher efficiencies.

Coming to the *input current* (drawn by the converter), for the hypothetical case of 100% efficiency, we get

$$I_{IN\_ideal} = I_O \times \left(\frac{V_O}{V_{IN}}\right)$$

So, in a real converter, the input current increases from its "ideal" value by the factor  $1/\eta$ .

$$I_{IN\_measured} = \frac{1}{\eta} \times I_{IN\_ideal}$$

Therefore, if we can achieve a high efficiency, the current drawn from the input (keeping application conditions unchanged) will decrease — *but only up to a point*. The input current clearly cannot fall below the "brickwall" that is "I<sub>IN ideal</sub>," because this current is

equal to  $P_O/V_{IN}$  — that is, related only to the 'useful power'  $P_O$ , delivered by the power supply, which we are assuming has not changed.

Further, since

$$V_O \times I_O = V_{IN} \times I_{IN ideal}$$

by simple algebra, the dissipation in the power supply (energy lost per second as heat) can also be written as

$$P_{loss} = V_{IN} \times (I_{IN \text{ measured}} - I_{IN \text{ ideal}})$$

This form of the dissipation equation indicates a little more explicitly how *additional* energy (more input current for a given input voltage) is pushed into the input terminals of the power supply by the applied dc source — to compensate for the wasted energy inside the power supply — even as the converter continues to provide the useful energy  $P_O$  being constantly demanded by the load.

A modern switching power supply's efficiency can typically range from 65 to 95% — that figure being considered attractive enough to have taken switchers to the level of interest they arouse today, and their consequent wide application. *Traditional regulators* (like the 'linear regulator') provide much poorer efficiencies — and that is the main reason why they are slowly but surely getting replaced by switching regulators.

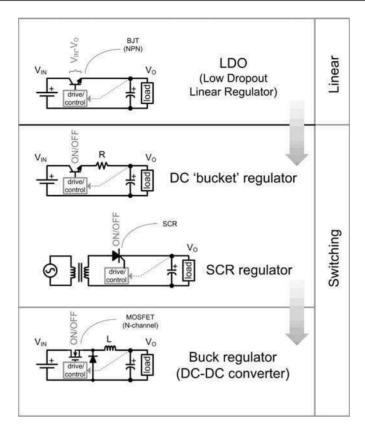

### Linear Regulators

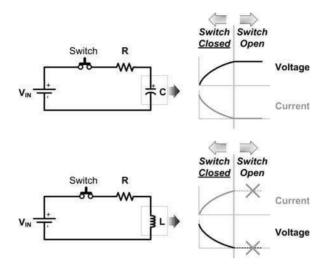

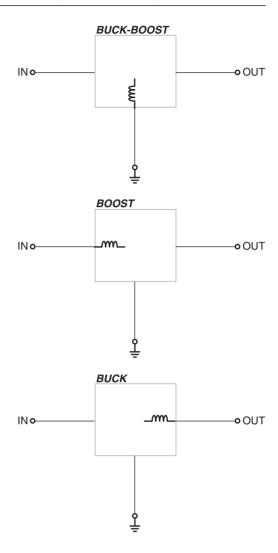

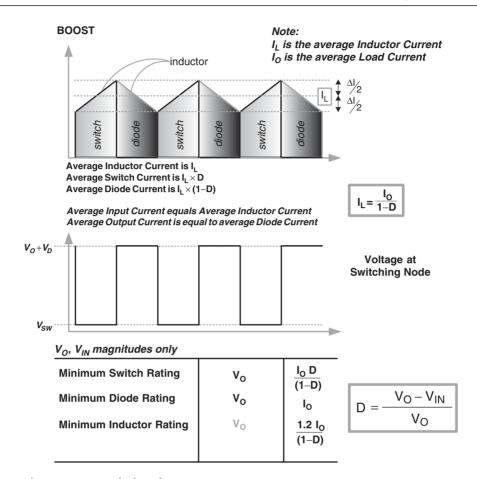

'Linear regulators,' equivalently called 'series-pass regulators,' or simply 'series regulators,' also produce a regulated dc output rail from an input rail. But they do this by placing a transistor in series between the input and output. Further, this 'series-pass transistor' (or 'pass-transistor') is operated in the *linear* region of its voltage-current characteristics — thus acting like a variable *resistance* of sorts. As shown in the uppermost schematic of *Figure 1-2*, this transistor is made to literally "drop" (abandon) the unwanted or "excess" voltage across itself.

The excess voltage is clearly just the difference ' $V_{IN} - V_O$ ' — and this term is commonly called the 'headroom' of the linear regulator. We can see that the headroom needs to be a *positive* number always, thus implying  $V_O < V_{IN}$ . Therefore, linear regulators are, in principle, always 'step-down' in nature — that being their most obvious limitation.

In some applications (e.g. battery powered portable electronic equipment), we may want the output rail to remain well-regulated even if the input voltage dips very low — say down to within 0.6 V or less of the set output level V<sub>O</sub>. In such cases, the minimum possible headroom (or 'dropout') achievable by the linear regulator stage may become an issue.

Figure 1-2: Basic Types of Linear and Switching Regulators

No switch is perfect, and even if held fully conducting, it does have some voltage drop across it. So the dropout is simply the minimum achievable 'forward-drop' across the switch. Regulators which can continue to work (i.e. regulate their output), with  $V_{\rm IN}$  barely exceeding  $V_{\rm O}$ , are called 'low dropout' regulators, or 'LDOs.' But note that there is really no precise voltage drop at which a linear regulator "officially" becomes an LDO. So the term is sometimes applied rather loosely to linear regulators in general. However, the rule-of thumb is that a dropout of about 200 mV or lower qualifies as an LDO, whereas older devices (conventional linear regulators) have a typical dropout voltage of around 2 V. There is also an intermediate category, called 'quasi-LDOs' that have a dropout of about 1 V, that is, somewhere in between the two.

Besides being step-down in principle, linear regulators have another limitation — poor efficiency. Let us understand why that is so. The instantaneous power dissipated in any device is by definition the cross-product  $V \times I$ , where V is the instantaneous voltage drop across it and I the instantaneous current through it. In the case of the series-pass transistor, under steady application conditions, both V and I are actually constant with respect to

time — V in this case being the headroom  $V_{IN}-V_O$ , and I the load current  $I_O$  (since the transistor is always in *series* with the load). So we see that the V × I dissipation term for linear regulators can, under certain conditions, become a significant proportion of the useful output power  $P_O$ . And that simply spells "poor efficiency"! Further, if we stare hard at the equations, we will realize there is also nothing we can do about it — how can we possibly argue against something as basic as V × I? For example, if the input is 12 V, and the output is 5 V, then at a load current of 100 mA, the dissipation in the regulator is necessarily  $\Delta V \times I_O = (12-5) \ V \times 100 \ mA = 700 \ mW$ . The useful (output) power is however  $V_O \times I_O = 5 \ V \times 100 \ mA = 500 \ mW$ . Therefore, the efficiency is  $P_O/P_{IN} = 500/(700 + 500) = 41.6\%$ . What can we do about that?!

On the positive side, linear regulators are very "quiet" — exhibiting none of the noise and EMI (electromagnetic interference) that have unfortunately become a "signature" or "trademark" of modern switching regulators. Switching regulators need *filters* — usually both at the input and the output, to quell some of this noise, which can interfere with other gadgets in the vicinity, possibly causing them to malfunction. Note that sometimes, the usual input/output capacitors of the converter may themselves serve the purpose, especially when we are dealing with 'low-power' (and 'low-voltage') applications. But in general, we may require filter stages containing *both* inductors and capacitors. Sometimes these stages may need to be cascaded to provide even greater noise attenuation.

## Achieving High Efficiency through Switching

Why are switchers so much more efficient than "linears"?

As their name indicates, in a *switching* regulator, the series transistor is not held in a perpetual *partially conducting* (and therefore dissipative) mode — but is instead *switched* repetitively. So there are only two *states* possible — either the switch is held 'ON' (fully conducting) or it is 'OFF' (fully non-conducting) — there is no "middle ground" (at least not in principle). When the transistor is ON, there is (ideally) zero *voltage* across it (V = 0), and when it is OFF we have zero *current* through it (I = 0). So it is clear that the cross-product 'V × I' is also zero for *either* of the two states. And that simply implies zero 'switch dissipation' at all times. Of course this too represents an impractical or "ideal" case. Real switches do dissipate. One reason for that they are never either *fully* ON nor *fully* OFF. Even when they are supposedly ON, they have a small voltage drop across them, and when they are supposedly "OFF," a small current still flows through them. Further, no device switches "instantly" either — there is a always definable period in which the device is *transiting between states*. During this interval too, V × I is not zero, and some additional dissipation occurs.

We may have noticed that in most introductory texts on switching power conversion, the switch is shown as a *mechanical* device — with contacts that simply open ("switch OFF")

or close ("switch ON"). So a mechanical device comes very close to our definition of a "perfect switch" — and that is the reason why it is often the vehicle of choice to present the most basic principles of power conversion. But one obvious problem with actually *using* a mechanical switch in any practical converter is that such switches can wear out and fail over a relatively short period of time. So in practice, we always prefer to use a *semiconductor device* (e.g. a transistor) as the switching element. As expected, that greatly enhances the life and reliability of the converter. But the most important advantage is that since a semiconductor switch has none of the mechanical "inertia" associated with a mechanical device, it gives us the ability to switch *repetitively* between the ON and OFF states — and do so *very fast*. We have already realized that that will lead to *smaller* components in general.

We should be clear that the phrase "switching fast," or "high switching speed," has slightly varying connotations, even within the area of switching power conversion. When it is applied to the overall *circuit*, it refers to the frequency at which we are repeatedly switching — ON OFF ON OFF and so on. This is the converter's basic *switching frequency* 'f' (in Hz). But when the same term is applied specifically to the *switching element* or device, it refers to the *time* spent transiting *between* its two states (i.e. from ON to OFF and OFF to ON), and is typically expressed in 'ns' (nanoseconds). Of course this transition interval is then rather *implicitly* and intuitively being compared to the total 'time period' T (where T = 1/f), and therefore to the switching frequency — though we should be clear there is no *direct* relationship between the transition time and the switching frequency.

We will learn shortly that the ability to *crossover* (i.e. transit) quickly between switching states is in fact rather crucial. Yes, up to a point, the switching speed is almost completely determined by how "strong" and effective we can make our external 'drive circuit.' But ultimately, the speed becomes limited purely by the device and its technology — an "inertia" of sorts at an electrical level.

# **Basic Types of Semiconductor Switches**

Historically, most power supplies used the 'bjt' (bipolar junction transistor) shown in *Figure 1-2*. It is admittedly a rather *slow* device by modern standards. But it is still relatively cheap! In fact its 'npn' version is even cheaper, and therefore more popular than its 'pnp' version. Modern switching supplies prefer to use a 'mosfet' (metal oxide semiconductor field effect transistor), often simply called a 'fet' (see *Figure 1-2* again). This modern high-speed switching device also comes in several "flavors" — the most commonly used ones being the *n-channel* and *p-channel* types (both usually being the 'enhancement mode' variety). The *n-channel mosfet* happens to be the favorite in terms of cost-effectiveness and performance, for most applications. However, sometimes, p-channel devices may be preferred for various reasons — mainly because they usually require simpler drive circuits.

Despite the steady course of history in favor of mosfets in general, there still remain some arguments for continuing to prefer bits in certain applications. Some points to consider and debate here are:

- lt is often said that it is *easier to drive a mosfet than a bjt*. In a bjt we do need a large drive current (injected into its 'base' terminal) to turn it ON. We also need to *keep* injecting base current to *keep it* in that state. On the other hand, a mosfet is considered easier to drive. In theory, we just have to apply a certain voltage at its 'gate' terminal to turn it ON, and also keep it that way. Therefore, a mosfet is called a 'voltage-controlled' device, whereas a bjt is considered a 'current controlled' device. However, in reality, a modern mosfet needs a certain amount of gate current *during* the time it is *in transit* (ON to OFF and OFF to ON). Further, to make it change state *fast*, we may in fact need to push in (or pull) out a *lot* of current (typically 1 to 2 A).

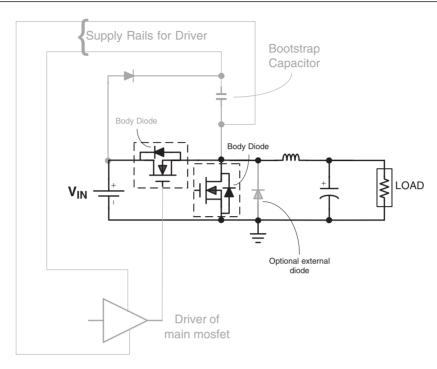

- b) The *drive requirements of a bjt may actually turn out easier to implement* in many cases. The reason for that is, to turn an npn bjt ON for example, its gate has to be taken only about 0.8 V above its emitter (and can even be tied directly to its collector on occasion). Whereas, in an n-channel mosfet, its gate has to be taken *several volts* higher than its source. Therefore, in certain types of dc-dc converters, when using an n-channel mosfet, it can be shown that we need a 'drive rail' that is significantly *higher* than the (available) input rail V<sub>IN</sub>. And how else can we hope to have such a rail except by a circuit that can somehow manage to "push" or "pump" the input voltage to a higher level? When thus implemented, such a rail is called the 'bootstrap' rail.

**Note:** The most obvious implementation of a 'bootstrap circuit' may just consist of a small capacitor that gets charged by the input source (through a small signal diode) whenever the switch turns OFF. Thereafter, when the switch turns ON, we know that certain voltage nodes in the power supply suddenly "flip" whenever the switch changes state. But since the 'bootstrap capacitor' continues to hold on to its acquired voltage (and charge), it automatically pumps the bootstrap rail to a level higher than the input rail, as desired. This rail then helps drive the mosfet properly under all conditions.

- c) The main advantage of bjts is that they are known to generate *significantly less EMI* and 'noise and ripple' than mosfets. That ironically is a positive outcome of their *slower* switching speed!

- d) Bjts are also often better suited for *high-current* applications because their 'forward drop' (*on-state voltage drop*) is *relatively constant*, even for very high switch currents. This leads to significantly lower 'switch dissipation,' more so when the switching frequencies are not too high. On the contrary, in a mosfet, the forward drop is almost proportional to the current passing through it so its dissipation can become significant at high loads. Luckily, since it also switches faster (lower transition times), it usually more than makes up, and so in fact becomes much better in terms of the *overall* loss more so when operated at very high switching frequencies.

11

**Note:** In an effort to combine the "best of both worlds," a "combo" device called the 'IGBT' (insulated gate bipolar transistor) is also often used nowadays. It is driven like a mosfet (voltage-controlled), but behaves like a bjt in other ways (the forward drop and switching speed). It too is therefore suited mainly for low-frequency and high-current applications, but is considered easier to drive than a bjt.

# Semiconductor Switches Are Not "Perfect"

We mentioned that all semiconductor switches suffer losses. Despite their advantages, they are certainly not the perfect or ideal switches we may have imagined them to be at first sight.

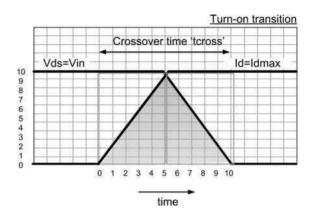

So for example, unlike a mechanical switch, in the case of a semiconductor device, we may have to account for the small but measurable 'leakage current' flowing through it when it is considered "fully OFF" (i.e. non-conducting). This gives us a dissipation term called the 'leakage loss.' This term is usually not very significant and can be ignored. However, there is a small but significant voltage drop ('forward drop') across the semiconductor when it is considered "fully ON" (i.e. conducting) — and that gives us a significant 'conduction loss' term. In addition, there is also a brief moment as we transition between the two switching states, when the current and voltage in the switch need to slew up or down almost simultaneously to their new respective levels. So, during this 'transition time' or 'crossover time,' we neither have V = 0 nor I = 0 instantaneously, and therefore nor is  $V \times I = 0$ . This therefore leads to some additional dissipation, and is called the 'crossover loss' (or sometimes just 'switching loss'). Eventually, we need to learn to minimize all such loss terms if we want to improve the efficiency of our power supply.

However, we must remember that power supply design is by its very nature full of *design tradeoffs* and subtle compromises. For example, if we look around for a transistor with a very low forward voltage drop, possibly with the intent of minimizing the conduction loss, we usually end up with a device that also happens to transition more slowly — thus leading to a higher crossover loss. There is also an overriding concern for cost that needs to be constantly looked into, particularly in the commercial power supply arena. So, we should not underestimate the importance of having an astute and seasoned engineer at the helm of affairs, one who can really grapple with the finer details of power supply design. As a corollary, neither can we probably ever hope to replace him or her (at least not entirely), by some smart automatic test system, nor by any "expert design software" that we may have been dreaming of.

# Achieving High Efficiency through the Use of Reactive Components

We have seen that one reason why switching regulators have such a high efficiency is because they use a *switch* (rather than a transistor that "thinks" it is a resistor, as in an LDO). Another root cause of the high efficiency of modern switching power supplies is their effective use of *both capacitors and inductors*.

Capacitors and inductors are categorized as 'reactive' components because they have the unique ability of being able to *store energy*. However, that is why they cannot ever be made to *dissipate* any energy either (at least not *within* themselves) — they just store any energy "thrown at them"! On the other hand, we know that 'resistive' components dissipate energy, but unfortunately, can't store any!

A capacitor's stored energy is called *electrostatic*, equal to  $\frac{1}{2} \times C \times V^2$  where C is the 'capacitance' (in Farads), and V the voltage across the capacitor. Whereas an inductor stores *magnetic* energy, equal to  $\frac{1}{2} \times L \times I^2$ , L being the 'inductance' (in Henries) and I the current passing through it (at any given moment).

But we may well ask — despite the obvious efficiency concerns, do we really *need* reactive components *in principle*? For example, we may have realized we don't really need an input or output capacitor for implementing a *linear regulator* — because the series-pass element is all that is required to block any excess voltage. For switching regulators however, the reasoning is rather different. This leads us to the general "*logic of switching power conversion*" summarized below.

- A transistor is needed to establish control on the output voltage, and thereby bring it into regulation. The reason we *switch* it is as follows dissipation in this control element is related to the product of the voltage across the control device and the current through it, that is V × I. So if we make either V or I zero (or very small), we will get zero (or very small) dissipation. By switching *constantly* between ON and OFF states, we can keep the switch dissipation down, but at the same time, by controlling the *ratio* of the ON and OFF intervals, we can *regulate* the output, based on average energy flow considerations.

- But whenever we switch the transistor, we effectively disconnect the input from the output (during either the ON or OFF state). However, the output (load) always demands a continuous flow of energy. Therefore we need to introduce energy storage elements somewhere inside the converter. In particular, we use output capacitors to "hold" the voltage steady across the load during the above-mentioned input-to-output "disconnect" interval.

- But as soon as we put in a capacitor, we now also need to limit the *inrush current* into it all capacitors connected directly across a dc source, will exhibit this uncontrolled inrush and that can't be good either for noise, EMI, or for efficiency. Of course we could simply opt for a *resistor* to subdue this inrush, and that in fact was the approach behind the early "bucket regulators" (*Figure 1-2*).

- But unfortunately a resistor always dissipates so what we may have saved in terms of switch dissipation, may ultimately end up in the resistor! To maximize the overall efficiency, we therefore need to use only reactive elements in the conversion

process. Reactive elements can *store* energy but do not dissipate any (in principle). Therefore, an *inductor becomes our final choice* (along with the capacitor), based on its ability to *non-dissipatively limit the (rate of rise) of current*, as is desired for the purpose of limiting the capacitor inrush current.

Some of the finer points in this summary will become clearer as we go on. We will also learn that *once the inductor has stored some energy, we just can't wish this stored energy away at the drop of a hat"*. We need to do something about it! And that in fact gives us an actual working converter down the road.

# Early RC-based Switching Regulators

As indicated above, a possible way out of the "input-to-output disconnect" problem is to use *only an output capacitor*. This can store some extra energy when the switch connects the load to the input, and then provide this energy to the load when the switch disconnects the load.

But we still need to limit the capacitor *charging current* ('inrush current'). And as indicated, we could use a resistor. That was in fact the basic principle behind some early linear-to-switcher "crossover products" like the 'bucket regulator' shown in *Figure 1-2*.

The bucket regulator uses a transistor driven like a *switch* (as in modern switching regulators), a small *series resistor* to limit the current (not entirely unlike a linear regulator), and an *output capacitor* (the "bucket") to store and then provide energy when the switch is OFF. Whenever the output voltage falls below a certain threshold, the switch turns ON, "tops up" the bucket, and then turns OFF. Another version of the bucket regulator uses a cheap low-frequency switch called an SCR ('semiconductor controlled rectifier') that works off the secondary windings of a step-down transformer connected to an ac mains supply, as also shown in *Figure 1-2*. Note that in this case, the resistance of the windings (usually) serves as the (only) effective limiting resistance.

Note also that in either of these RC-based bucket regulator implementations, the switch ultimately ends up being *toggled repetitively* at a certain rate — and in the process, a rather crudely regulated stepped down output dc rail is created. By definition, that makes these regulators *switching regulators* too!

But we realize that the very use of a resistor in any power conversion process always bodes ill for efficiency. So, we may have just succeeded in *shifting* the dissipation away from the transistor — into the resistor! If we really want to maximize overall efficiency, we need to do away with *any intervening resistance* altogether.

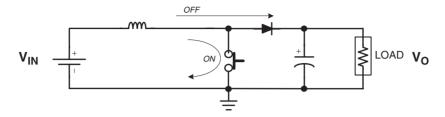

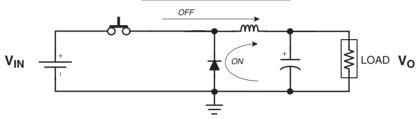

So we attempt to use an inductor instead of a resistor for the purpose — we don't really have many other component choices left in our bag! In fact, if we manage to do that, we get our first modern *LC-based switching regulator* — the 'buck regulator' (i.e. step-down converter), as also presented in *Figure 1-2*.

# **LC-based Switching Regulators**

Though the detailed functioning of the modern buck regulator of *Figure 1-2* will be explained a little later, we note that besides the obvious replacement of R with an L, it looks very similar to the bucket regulator — *except for a "mysterious" diode*. The basic principles of power conversion will in fact become clear only *when we realize the purpose of this diode*. This component goes by several names — 'catch diode,' 'freewheeling diode,' 'commutation diode,' and 'output diode,' to name a few! But its basic purpose is always the same — a purpose we will soon learn is intricately related to the behavior of the *inductor* itself.

Aside from the buck regulator, there are *two* other ways to implement the basic goal of switching power conversion (using *both inductors and capacitors*). Each of these leads to a distinct 'topology.' So besides the *buck* (step-down), we also have the 'boost' (step-up), and the 'buck-boost' (step-up or step-down). We will see that though all these are based on the same *underlying* principles, they are set up to look and behave quite differently. As a prospective power supply designer, we really do need to learn and master each of them almost on an *individual basis*. We must also keep in mind that in the process, our *mental picture will usually need a drastic change as we go from one topology to another*.

**Note:** There are some other capacitor-based possibilities — in particular 'charge pumps' — also called 'inductor-less switching regulators.' These are usually restricted to rather low powers and produce output rails that are rather crudely regulated *multiples* of the input rail. In this book, we are going to ignore these types altogether.

Then there are also some other types of LC-based possibilities — in particular the 'resonant topologies.' Like conventional dc-dc converters, these also use both types of reactive components (L and C) along with a switch. However, their basic principle of operation is very different. Without getting into their actual details, we note that these topologies do not maintain a constant switching frequency, which is something we usually rather strongly desire. From a practical standpoint, any switching topology with a variable switching frequency, can lead to an unpredictable and varying EMI spectrum and noise signature. To mitigate these effects, we may require rather complicated filters. For such reasons, resonant topologies have not really found widespread acceptance in commercial designs, and so we too will largely ignore them from this point on.

### The Role of Parasitics

In using conventional LC-based switching regulators, we may have noticed that their constituent inductors and capacitors do get fairly *hot* in most applications. But if, as we said, these components are *reactive*, why at all are they getting hot? We need to know why, because any source of heat impacts the overall efficiency! And *efficiency* is what modern switching regulators are all about!

The heat arising from *real-world* reactive components can invariably be traced back to dissipation occurring within the small 'parasitic' *resistive* elements, which always accompany any such (reactive) component.

For example, a real inductor has the basic property of inductance L, but it also has a certain non-zero *dc resistance* ('DCR') term, mainly associated with the copper windings used. Similarly, any real capacitor has a capacitance C, but it also has a small *equivalent series resistance* ('ESR'). Each of these terms produces 'ohmic' losses — that can all add up and become fairly significant.

As indicated previously, a real-world semiconductor switch can also be considered as having a parasitic resistance "strapped" *across* it. This parallel resistor in effect "models" the leakage current path, and thus the 'leakage loss' term. Similarly, the forward drop across the device can also, in a sense, be thought of as a *series* parasitic resistance — leading to a conduction loss term.

But any real-world component also comes along with various *reactive* parasitics. For example an inductor can have a significant parasitic capacitance across its terminals — associated with electrostatic effects between the layers of its windings. A capacitor can also have an *equivalent series inductance* ('ESL') — coming from the small inductances associated with its leads, foil, and terminations. Similarly, a mosfet also has various parasitics — for example the "unseen" capacitances present *between* each of its terminals (within the package). In fact, these mosfet parasitics play a major part in determining the limits of its switching speed (transition times).

In terms of dissipation, we understand that reactive parasitics certainly cannot dissipate heat — at least not *within the parasitic element itself*. But more often than not, these reactive parasitics do manage to "dump" their stored energy (at specific moments during the switching cycle) into a nearby *resistive* element — thus increasing the overall losses indirectly.

Therefore we see that to improve efficiency, we generally need to go about minimizing all such parasitics — *resistive or reactive*. We should not forget they are the very reason we are not getting 100% efficiency from our converter in the first place. Of course, we have to learn to be able to do this optimization to within *reasonable* and *cost-effective* bounds, as dictated by market compulsions and similar constraints.

But we should also bear in mind that *nothing is so straightforward in power*! So these parasitic elements should not be considered entirely "useless" either. In fact they do play a rather helpful and stabilizing role on occasion.

- For example, if we short the outputs of a dc-dc converter, we know it is unable to regulate, however hard it tries. In this 'fault condition' ('open-loop'), the momentary 'overload current' within the circuit can be "tamed" (or mitigated) a great deal by the very presence of certain identifiably "friendly" parasitics.

- We will also learn that the so-called 'voltage-mode control' switching regulators actually *rely on the ESR* of the output capacitor for ensuring 'loop stability' even under normal operation. As indicated previously, loop stability refers to the ability of

a power supply to regulate its output quickly, when faced with sudden changes in line and load, without undue oscillations or ringing.

Certain other parasitics however may just prove to be a nuisance and some others a sheer bane. But their actual *roles too may keep shifting*, depending upon the prevailing conditions in the converter. For example

- A certain parasitic *inductance* may be quite *helpful* during the *turn-on* transition of the switch by acting to limit any current spike trying to pass through the switch. But it can be *harmful* due to the high *voltage spike* it creates across the switch at *turn-off* (as it tries to release its stored magnetic energy).

- On the other hand, a parasitic *capacitance* present across the switch for example, can be *helpful* at *turn-off* but *unhelpful* at *turn-on*, as it tries to dump its stored electrostatic energy inside the switch.

**Note:** We will find that during turn-off, the parasitic capacitance mentioned above helps limit or 'clamp' any potentially destructive voltage spikes appearing across the switch, by *absorbing* the energy residing in that spike. It also helps *decrease the crossover loss* by slowing down the rising ramp of voltage, and thereby reducing the V-I "overlap" (between the transiting V and I waveforms of the switch). However at *turn-on*, the same parasitic capacitance now has to discharge whatever energy it acquired during the preceding turn-off transition — and that leads to a *current spike* inside the switch. Note that this spike is externally "invisible" — apparent only by the higher-than-expected switch dissipation, and the resulting higher-than-expected temperature.

Therefore, generally speaking, *all parasitics constitute a somewhat "double-edged sword*," one that we just can't afford to overlook for very long in *practical* power supply design. However, as we too will do in some of our discussions that follow, sometimes we can consciously and *selectively* decide to ignore some of these second-order influences initially, just to build up *basic concepts* in power first. Because the truth is if we don't do that, we just run the risk of feeling quite overwhelmed, too early in the game!

### Switching at High Frequencies

In attempting to generally reduce parasitics and their associated losses, we may notice that these are often dependent on various external factors — *temperature* for one. Some losses increase with temperature — for example the conduction loss in a mosfet. And some may decrease — for example the conduction loss in a bjt (*when operated with low currents*). Another example of the latter type is the ESR-related loss of a typical aluminum electrolytic capacitor, which also decreases with temperature. On the other hand, some losses may have rather "strange" shapes. For example, we could have an inverted "bell-shaped" curve — representing an optimum operating point somewhere *between the two extremes*. This is what the 'core loss' term of many modern 'ferrite' materials (used for inductor cores) looks like — it is at its minimum at around 80 to 90°C, increasing on either side.

From an overall perspective, it is hard to predict how all these variations with respect to temperature add up — and how the efficiency of the power supply is thereby affected by changes in temperature.

Coming to the dependency of parasitics and related loss terms on *frequency*, we do find a somewhat clearer trend. In fact it is rather rare to find any loss term that *decreases* at higher frequencies (though a notable exception to this is the loss in an aluminum electrolytic capacitor — because its ESR decreases with frequency). Some of the loss terms are virtually *independent* of frequency (e.g. conduction loss). And the remaining losses actually *increase* almost *proportionally* to the switching frequency — for example, the crossover loss. So in general, we realize that *lowering*, *not increasing*, *the switching frequency would almost invariably help improve efficiency*.

There are other frequency-related issues too, besides efficiency. For example, we know that switching power supplies are inherently noisy, and generate a lot of EMI. By going to higher switching frequencies, we may just be making matters worse. We can mentally visualize that even the small connecting wires and 'printed circuit board' (PCB) traces become very effective antennas at high frequencies, and will likely spew out *radiated EMI* in every direction.

This therefore begs the question: why at all are we face to face with a modern trend of ever-increasing switching frequencies? Why should we not decrease the switching frequency?

The first motivation toward higher switching frequencies was to simply take "the action" beyond audible human hearing range. Reactive components are prone to creating sound pressure waves for various reasons. So, the early LC-based switching power supplies switched at around 15–20 kHz, and were therefore barely audible, if at all.

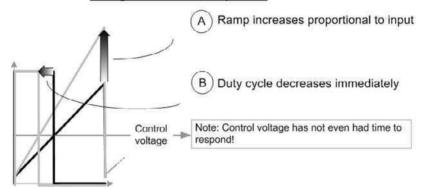

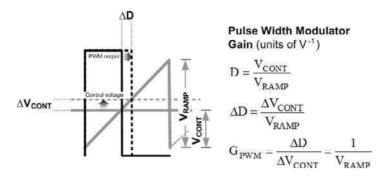

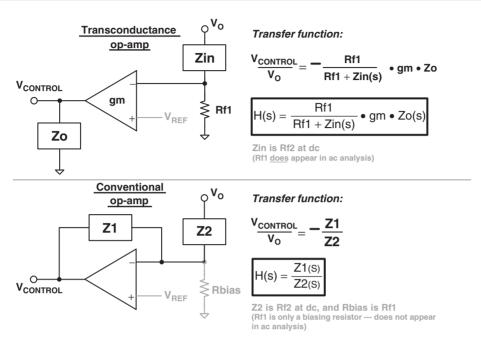

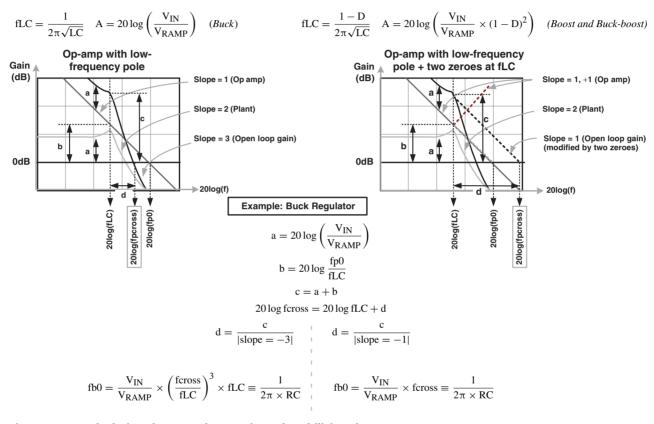

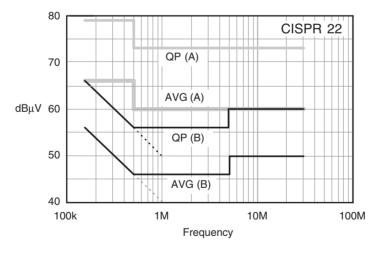

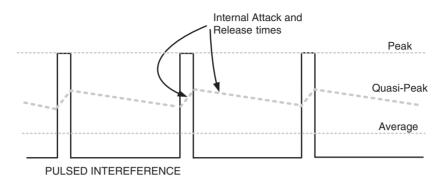

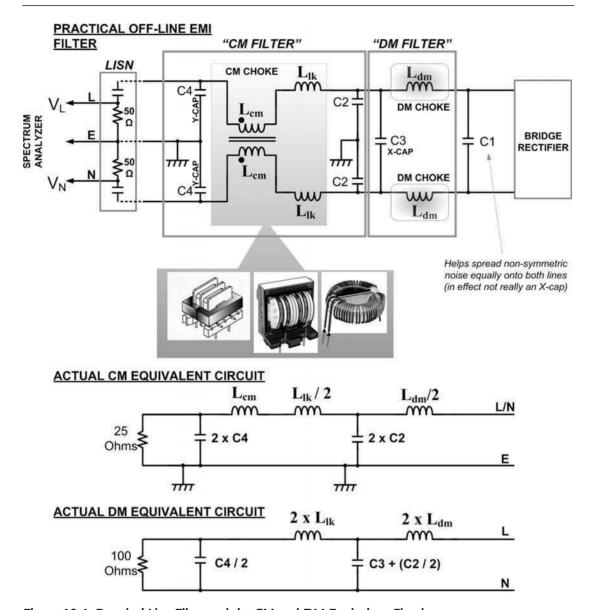

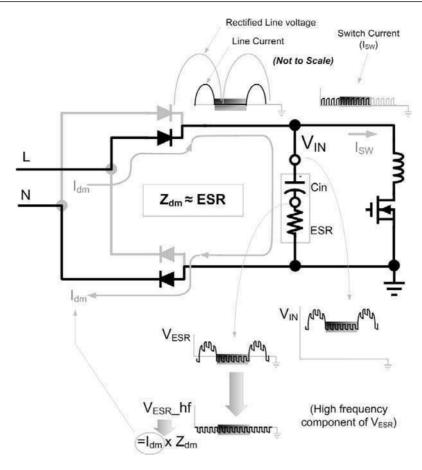

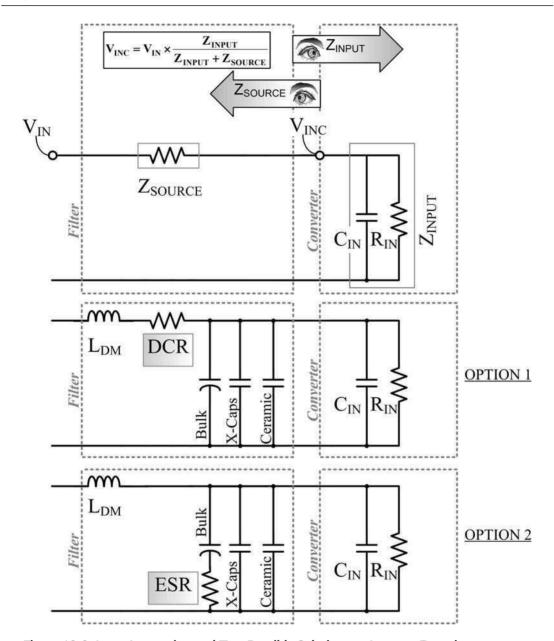

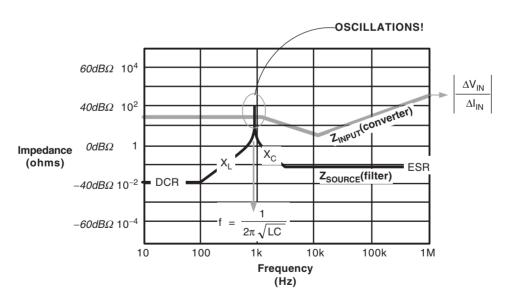

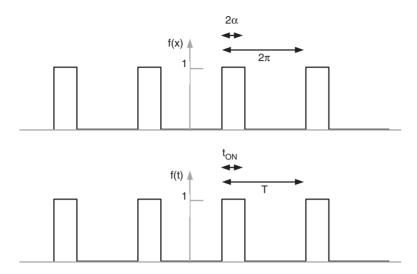

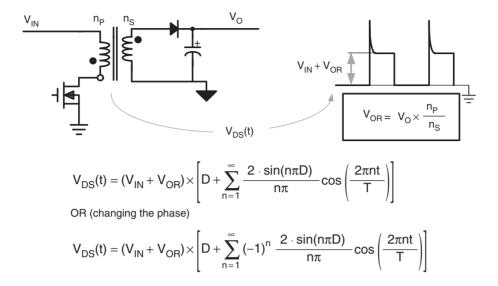

The next impetus toward even higher switching frequencies came with the realization that the bulkiest component of a power supply, that is, *the inductor, could be almost proportionately reduced in size if the switching frequency was increased* (everybody does seem to want smaller products, after all!). Therefore, successive generations of power converters moved upward in almost arbitrary steps, typically 20 kHz, 50 kHz, 70 kHz, 100 kHz, 150 kHz, 250 kHz, 300 kHz, 500 kHz, 1 MHz, 2 MHz, and often even higher today. This actually helped simultaneously *reduce* the size of the *conducted EMI* and input/output filtering components — including the capacitors! High switching frequencies can also almost proportionately enhance the *loop response* of a power supply.